---

## НОВЫЕ РАДИОЭЛЕКТРОННЫЕ СИСТЕМЫ И ЭЛЕМЕНТЫ

---

УДК 621.372

# РЕАЛИЗАЦИЯ ВОЗМОЖНОСТИ ПРОЕКТИРОВАНИЯ АНАЛОГОВЫХ ЭЛЕМЕНТОВ С ПРИМЕНЕНИЕМ ЛОГИЧЕСКИХ МИКРОСХЕМ

© 2025 г. П. С. Мартынов

Научно-технологический центр уникального приборостроения РАН,

ул. Бутлерова, 15, Москва, 117342 Российская Федерация

\*E-mail: La3232@mail.ru

Поступила в редакцию 20.12.2023 г.

После доработки 29.12.2023 г.

Принята к публикации 15.01.2024 г.

Представлено описание и применение методики синтеза радиотехнических элементов на конкретной задаче с использованием необходимой цифровой элементной базы для реализации аналоговых устройств. С помощью данной методики синтезированы аналоговые устройства и проведены экспериментальные исследования, получены выходные характеристики.

**Ключевые слова:** ПЛИС, АЦП, ЦАП, цифровая электроника, аналоговая электроника, элементарные звенья теории автоматического управления, системы передачи информации, дифференциальные уравнения, аналоговые микросхемы

**DOI:** 10.31857/S0033849425010114, **EDN:** HIOURF

### 1. ПОСТАНОВКА ЗАДАЧИ

В настоящее время цифровая электроника практически вытеснила аналоговую в бытовом и промышленном применении. Успешное развитие цифровой электроники стало возможным, потому что за последние времена была доработана теория проектирования логических систем. За основу теории была принята булева алгебра. В этом случае процесс проектирования цифрового устройства, заключается в составлении схемы из логических ячеек, соединенных между собой. Каждая ячейка выполняет определенную логическую операцию. В дальнейшем для схемы из логических ячеек формируют управляющую программу на специальном языке и перепрограммируют ее в память быстро действующей цифровой микросхемы.

В аналоговой электронике ведутся разработки по реализации интегральной микросхемы, которая позволяла бы синтезировать устройства составленных из определенного набора звеньев.

Чтобы решить эту задачу необходимо создание математической теории для проектирования аналоговых устройств, которая будет прототипом, для реализации цифровых микросхем. Анализ работ А. А. Харкевича [1], В. Н. Ильина [2], Ю. И. Топчева [3], выполненный Г. Т. Мишиным, позволил найти доказательство возможности применения систем линейных дифференциальных уравнений

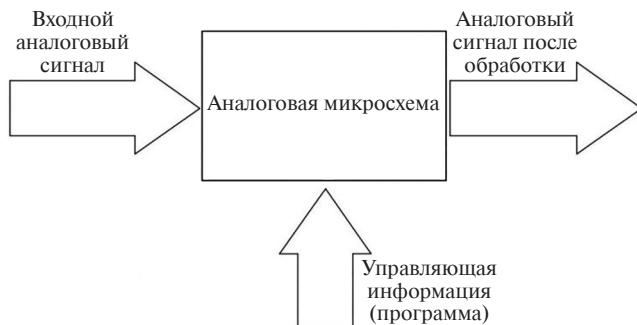

для математического описания базовых аналоговых устройств. Он предложил выделить наиболее часто встречающиеся математические функции и рассматривать их в качестве элементарных звеньев [4, 5]. Элементарные звенья являются элементами теории автоматического управления (ТАУ), а именно: дифференцирующим, интегрирующим, пропорциональным, звеном сложения или умножения и звеном мультиплексирования (соединения или разъединения). Найденную в результате решения системы уравнений ТАУ передаточную функцию следует разбить на части и в итоге полученное выражение должно состоять из элементарных звеньев. Этот подход может быть использован для проектирования аналоговых логических микросхем, которые позволяют обрабатывать аналоговые данные с использованием управляющей программы (рис. 1).

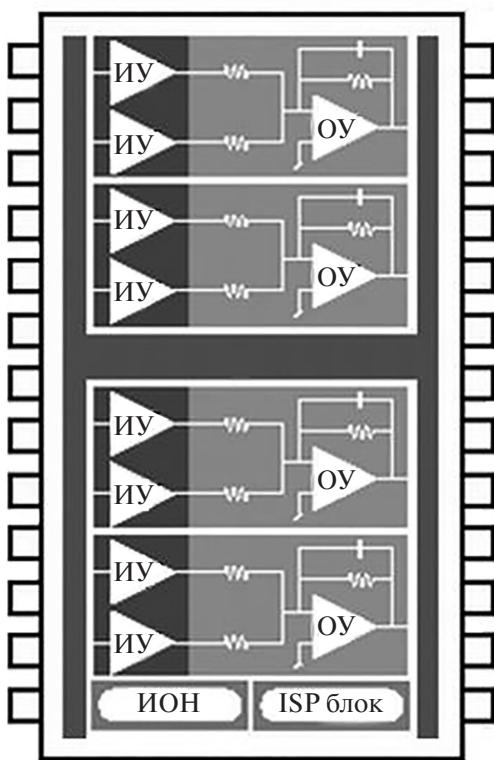

Аналоговые логические микросхемы подразделяются на матричные аналоговые большие интегральные схемы и на программируемые аналоговые интегральные схемы. На рис. 2 представлена обобщенная структурная схема аналоговой интегральной микросхемы, которая включает в себя операционные усилители (ОУ), инструментальные усилители (ИУ), компаратор, источник опорного напряжения (ИОН), цифро-аналоговый преобразователь, блок внутрисистемного программирования (ISP).

Рис. 1. Структурная схема аналоговой микросхемы.

Рис. 2. Структурная схема аналоговой интегральной микросхемы.

Описанные выше идеи было предложено реализовать на программируемой логической интегральной схеме (ПЛИС), где данные элементы будут работать на цифровой элементной базе по аналоговому прототипу, с возможностью многократного обновления управляющей программы для ПЛИС. Работа микросхемы ПЛИС по аналоговому прототипу подразумевает использование управляющего кода, в котором программно будут реализованы аналоговые устройства из элементарных звеньев. Данный код, написанный на языках программирования Verilog или VHDL, будет перепрограммироваться в энергонезависимую память ПЛИС. При успешном налаживании процесса разработки новой аналоговой элементной базы, данная методика может применяться для проектирования аналоговых устройств, которые необходимы для современных систем связи и передачи информации.

## 2. ТЕОРЕТИЧЕСКАЯ ЧАСТЬ

Анализ упомянутых выше работ, а также теоретических разработок в области ТАУ позволил выдвинуть идею о применении элементарных звеньев для проектирования некоторых аналоговых элементов и устройств. В перспективе это могло бы привести к созданию более простых схемотехнических решений, уменьшению стоимости и времени изготовления этих элементов и устройств. Для реализации указанной идеи была использована технология проектирования устройств на логических микросхемах, а именно: решение систем уравнений в матричной форме, применение правил построения цепей из элементов ТАУ, моделирование аналоговых цепей, программирование логических цифровых микросхем, обработка полученных результатов [4, 5].

Применяемые в методике элементарные звенья включают в себя интегрирующие, дифференцирующие, пропорциональное, а также звено сложения вычитания и умножения деления. Данные элементы представлены в табл. 1.

Описание звеньев в табл. 1 является упрощенным и не зависит от модели описываемого

Таблица 1. Математическое описание элементарных звеньев

| Элементарное звено | Передаточная функция           | Уравнение                   |

|--------------------|--------------------------------|-----------------------------|

| Интегрирующее      | $W(s) = \frac{k}{s}$           | $\frac{dy(t)}{dt} = ku(t)$  |

| Дифференцирующее   | $W(s) = ks$                    | $y(t) = k \frac{du(t)}{dt}$ |

| Пропорциональное   | $W(s) = \frac{y(s)}{u(s)} = k$ | $y(t) = ku(t)$              |

процесса. В ТАУ для описания передаточных функций используются дифференциальные уравнения, поэтому в предлагаемой методике проектирования элементарные звенья состоят из передаточных функций. Форма записи в виде уравнения нужна для составления структурной матрицы, далее на основе математического выражения формируется модель из группы аналоговых элементов.

В процессе получения передаточных функций моделей, когда интеграл или производную вычислить аналитически трудно, возможно применять численное интегрирование или дифференцирование (формула прямоугольников, формула трапеций, метод Ньютона–Котеса, метод Монте–Карло) [3–5]. Операцию по численному интегрированию применяют также и в случае, если производная от функции  $f(x)$  является сложной для дальнейшего преобразования. Необходимо отметить, что подход численного интегрирования хорошо определен и это способствует минимальной погрешности при вычислениях.

Поскольку интегрирующее, дифференцирующее и пропорциональное звенья могут быть представлены в матричной форме, приведем пример составления системы линейных неоднородных уравнений, записанных в виде структурной матрицы

$$\begin{aligned} a_{11}x_1 + a_{12}x_2 + \dots + a_{1n}x_n &= h_{11}f_1; \\ a_{21}x_1 + a_{22}x_2 + \dots + a_{2n}x_n &= h_{22}f_2; \\ \dots \\ a_{n1}x_1 + a_{n2}x_2 + \dots + a_{nn}x_n &= h_{nn}f_n. \end{aligned} \quad (1)$$

Такие матрицы необходимы для дальнейшего процесса моделирования и составления схемы из элементарных звеньев.

Если допустить, что в приведенной выше системе уравнений, коэффициенты  $a_{ij}$ ,  $h_{ik}$  являются дифференциальными полиномами, то получим систему дифференциальных уравнений, которая после процесса разложения на блоки должна стать моделью аналогового устройства.

Рассмотрим пример получения структурной схемы аналогового устройства по заданной математической модели, которая состоит из системы дифференциальных уравнений в форме преобразований Лапласа [4]

$$\begin{aligned} x_0 &= g, \\ x_1 &= x_0 - 4x_2/s, \\ x_2 &= 8x_1/s, \\ x_3 &= x_2 - 5x_4/s, \\ x_4 &= 100x_3/s. \end{aligned} \quad (2)$$

Используя правила разложения дифференциальных уравнений на полиномы из элементарных звеньев, составим структурную матрицу этой системы и выделим стрелками матричные циклы [5].

Далее перейдем от системы уравнений (2) к записи в матричной форме, которая представлена в табл. 2.

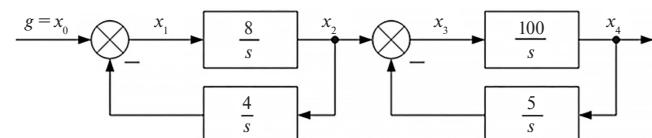

Применяя значения коэффициентов из таблицы, определим структурную схему устройства, которая после дальнейших преобразований представлена на рис. 3.

Полученная структурная схема состоит из четырех интегрирующих звеньев с различными передаточными функциями и двух звеньев сложения/вычитания. Данная система обладает также двумя отрицательными обратными связями:  $x_2 \rightarrow x_1$  и  $x_4 \rightarrow x_3$  соответственно [4, 5].

### 3. ПРАКТИЧЕСКАЯ ЧАСТЬ

Для подтверждения описанной выше теоретической была разработана печатная плата на основе программируемой логической микросхемы. Внешний вид печатного узла представлен на рис. 4.

Данная отладочная плата состоит из следующих компонентов: микросхема ПЛИС модели Altera Stratix V, а также аналого-цифровой преобразователь (АЦП), цифро-аналоговый преобразователь (ЦАП), микросхемы памяти и вспомогательная

**Таблица 2.** Процесс перехода к матричной форме записи системы уравнений

| $x_0$ | $x_1$ | $x_2$ | $x_3$ | $x_4$ |

|-------|-------|-------|-------|-------|

| 1     | 0     | 0     | 0     | 0     |

| 1     | -1    | -4/s  | 0     | 0     |

| 0     | 8/s   | -1    | 0     | 0     |

| 0     | 0     | 1     | -1    | -5/s  |

| 0     | 0     | 0     | 100/s | -1    |

**Рис. 3.** Структурная схема устройства из элементарных звеньев.

**Рис. 4.** Внешний вид печатного узла.

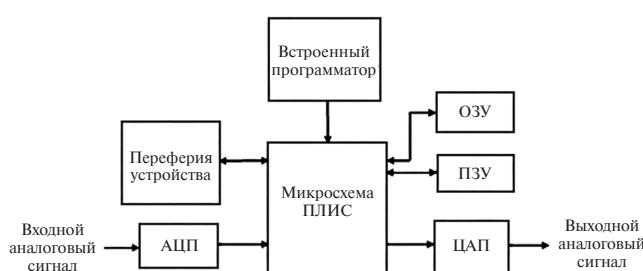

электроника, состоящая из фильтров питания, согласующих цепей, кварцевых генераторов, разъемов для входного и выходного сигналов. В энергонезависимую память была загружена программа через программатор. Данная программа представляла собой код, написанный на языке программирования VHDL/Verilog. Этот код описывал функционирование элементарных звеньев и являлся прототипом аналогового устройства, реализованного на цифровой элементной базе [6, 7]. Структурная схема представлена на рис. 5.

Исходный аналоговый сигнал поступает на АЦП и преобразуется в 12-разрядный цифровой сигнал, который затем поступает на ПЛИС. В ПЛИС находится программа обработки цифровых данных, которая преобразует поступающий цифровой сигнал и выдает его на ЦАП, в котором происходит обратное преобразование цифрового сигнала в аналоговый.

Для получения более полной информации о процессах преобразования сигналов на плате также установлены восьмибитные микросхемы памяти ОЗУ и ПЗУ для хранения промежуточных данных и данных программ. Кроме того, предусмотрены интерфейсы RS232- и JTAG для возможности перепрограммирования и внешнего подключения. Питание платы осуществляется от питания +5 В.

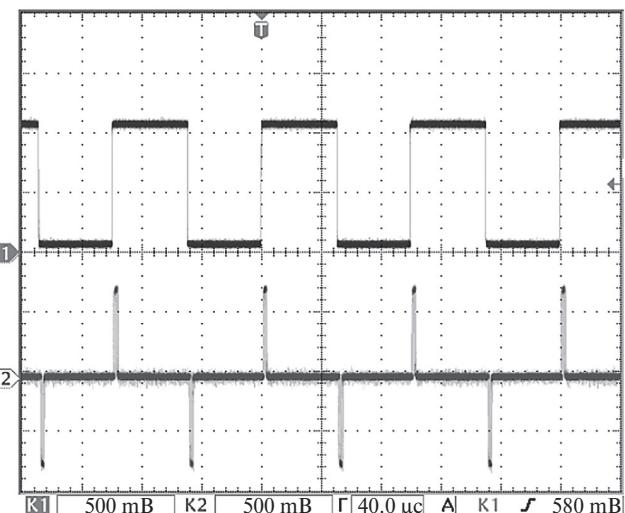

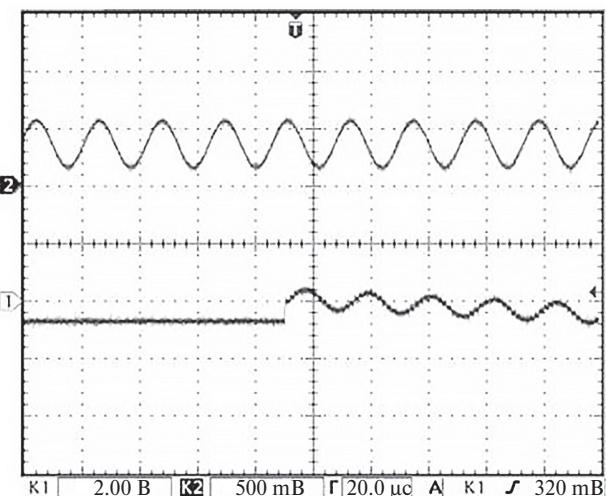

На вход устройства подавались различные сигналы: единичный импульс, ступенчатый сигнал, меандр, гармонический сигнал. Отклики некоторых звеньев на тестовые сигналы представлены в виде осциллограмм, которые отображаются на экране цифрового осциллографа. На рис. 6 отображена реакция для дифференцирующего звена, а на рис. 7 – для интегрирующего звена.

## ЗАКЛЮЧЕНИЕ

Разработан экспериментальный стенд для исследования элементарных звеньев и дальнейшей возможности проектирования радиотехнических устройств, составленных из этих звеньев. Представлена методика реализации аналоговых элементов на основе элементарных звеньев, а также

Рис. 5. Структурная схема устройства для отладки.

Рис. 6. Осциллограмма для дифференцирующего звена при прохождении меандра, с частотой 10 кГц.

Рис. 7. Осциллограмма для интегрирующего звена при прохождении гармонического сигнала с частотой 50 кГц.

разработаны управляющие программы для отладочной платы, с помощью которой проведены экспериментальные измерения.

Проведенные измерения позволяют сделать заключение что предложенную методику на основе предлагаемой аналоговой элементной базы, возможно применять для проектирования аналоговых интегральных микросхем.

## СПИСОК ЛИТЕРАТУРЫ

1. Ильин В.Н. Машинное проектирование электронных схем. М.: Энергия, 1972.

2. Харкевич А.А. Радиотехнические цепи и сигналы. М.: Наука, 1965.

3. Топчев Ю.И. Атлас для проектирования систем автоматического регулирования. Учеб. пособие для студентов вузов. М.: Машиностроение, 1989.

4. Мишин Г.Т. Естественно-научные основания аналоговой микроэлектроники. М.: МИЭМ, 2003.

5. Мишин Г.Т. // Наукоемкие технологии. 2004. Т. 5. № 2–3. С. 85.

6. Мартынов П.С. // РЭ. 2018. Т. 63. № 11. С. 1197.

7. Мартынов П.С. // РЭ. 2022. Т. 67. № 8. С. 825.

## IMPLEMENTATION OF THE POSSIBILITY OF ANALOG ELEMENTS DESIGN

© 2025 P.S. Martyanov

*Scientific and Technological Center of Unique Instrumentation of the RAS,

Butlerova Str., 15, Moscow, 117342 Russian Federation

E-mail: La3232@mail.ru*

Received December 20, 2023; revised December 29, 2023; accepted January 15, 2024

A brief description and application of the method of synthesizing radio engineering elements on a specific task using the necessary digital element base for implementing analog devices is presented. Using this method, analog devices were synthesized and experimental studies were carried out, output characteristics were obtained.

**Keywords:** PLD, DAC, ADC, ROM, digital electronics, analog electronics, elementary elements of automatic control theory, information transmission systems, differential equations, analog microcircuits